Chips Omicrono

La batería de tu móvil durará una semana con lo nuevo de IBM y Samsung

Samsung e IBM han presentado un nuevo diseño para el apilamiento de transistores en chips, que reduce el consumo energético y rompe limitaciones de rendimiento.

Noticias relacionadas

Aunque la crisis de componentes y semiconductores siga en su peor momento tanto en España como en el resto del mundo, eso no implica que no se hagan avances en este campo. Es lo que han conseguido Samsung e IBM, que han presentado un nuevo diseño para el apilamiento de transistores para chips de todo tipo.

Según recoge Engadget, tanto Samsung como IBM han presentado este diseño en el International Electron Devices Meeting o IEDM en San Francisco, Estados Unidos. Este nuevo diseño, aplicable a chips como sistemas en chip (System on a Chip o SoC) así como a procesadores modernos tendrá importantes ventajas, como una reducción del consumo energético.

Además de esto, este diseño permitiría a los fabricantes superar la Ley de Moore. Esta determina que cada dos años, aproximadamente, se duplica el número de transistores ubicados en un microprocesador estándar en la misma superficie. Por si fuera poco, este diseño también incluye mejoras en rendimiento o autonomía.

Nuevo diseño de transistores

Actualmente, el diseño por el cual se apilan los transistores sobre un chip en la mayoría de ocasiones implica que estos se apilan de forma horizontal, consiguiendo que la corriente vaya de lado a lado en el chip. El nuevo diseño presentado por IBM y Samsung cambia esta filosofía y su propio nombre lo indica: Vertical Transport Field Effect Transistors o VTFET.

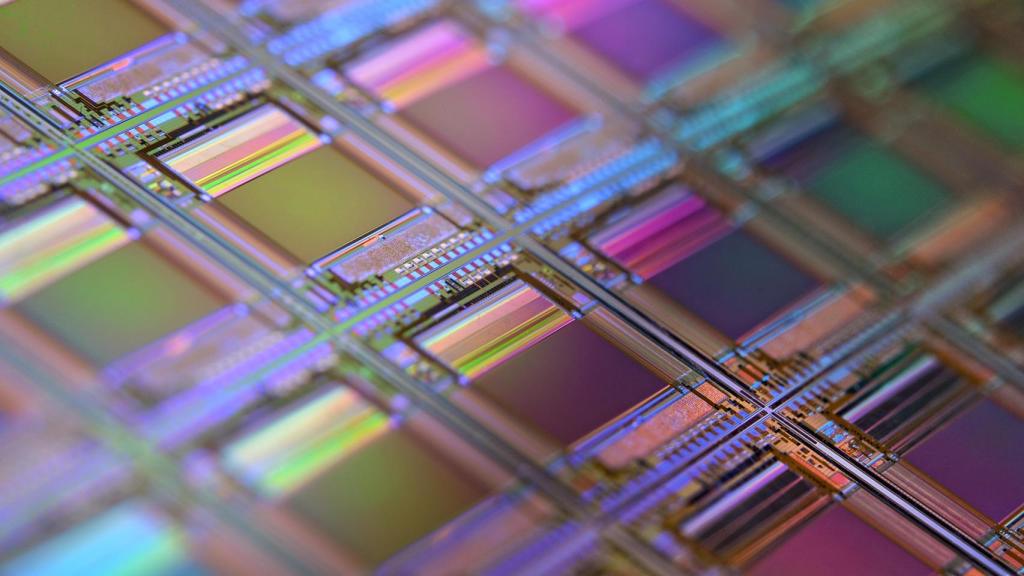

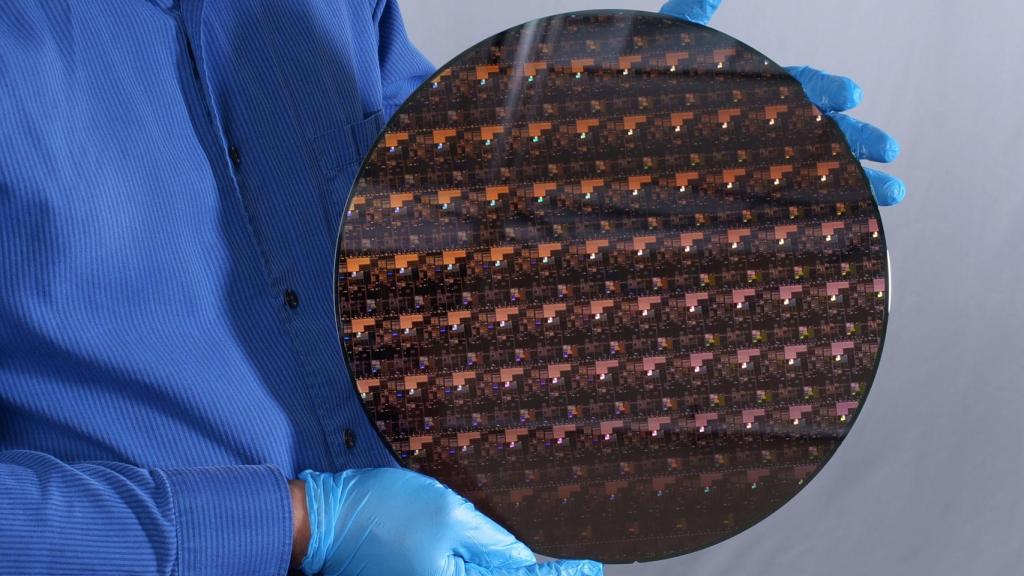

Chips de 2 nm de IBM Omicrono

Con este diseño, los transistores pasan de estar apilados en forma horizontal a perpendicular. Es decir, que la corriente deja de transportarse de lado a lado y lo hace de forma vertical. El diseño VTFET, por tanto, permite conseguir chips hasta el doble de rápidos, o conseguir que el consumo energético en un 85%, gracias de nuevo a la posibilidad de ir más allá de la Ley de Moore.

Tardará en verse

Y es que IBM y Samsung prometen que al superar estas limitaciones, también se superan limitaciones de rendimiento establecidas por el diseño estándar. Ahora bien, hay que aclarar que este diseño tiene una contrapartida: que dichas mejoras deben aplicarse o en el campo de la autonomía o en el rendimiento.

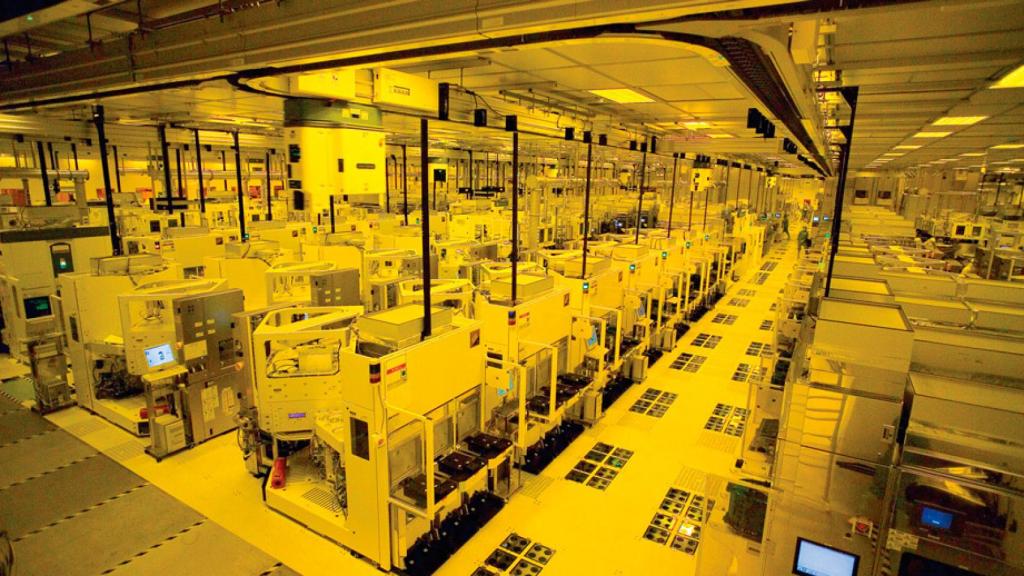

Fábrica de procesadores TSMC.

Así lo ha explicado Samsung, concretando que estas mejoras no se podrán dar en ambos apartados. También ha explicado que este diseño no implicará conseguir chips más densos de 1 nanómetro. De forma proporcional, ambas compañías han querido resaltar las muchas mejoras que implica VTFET, llegando a afirmar que la criptominería sería un proceso mucho más eficiente y que los smartphones que adopten este diseño podrían durar una semana con tan solo una carga de batería.

Desgraciadamente, pasará un tiempo hasta que se vea en el mercado. Ni IBM ni Samsung han querido explicar cuándo llevarán al mercado VTFET, y tampoco es posible determinar cuándo los fabricantes optarán por este diseño.