SiPearl es el diseñador del microprocesador que equipará el superordenador europeo de exaescala.

Europa se prepara para la fabricación de procesadores de alto rendimiento con tecnología propia

Un consorcio de 28 socios ha completado la primera fase de desarrollo y ya se ha realizado una prueba de concepto con la conducción autónoma.

3 enero, 2022 03:06Noticias relacionadas

En la carrera por desplegar supercomputadores de exaescala –aquellas capaces de superar la potencia de procesamiento del cerebro humano a escala neuronal–, la Unión Europea puso en marcha en 2018 el proyecto European Processor Initiative (EPI).

Su primer objetivo era el diseño y desarrollo, en tres años, de chips europeos de bajo consumo para la computación de alto rendimiento (HPC, por sus siglas en inglés). La primera generación de estos semiconductores debía estar lista a finales de este año 2021. Y el calendario se ha cumplido.

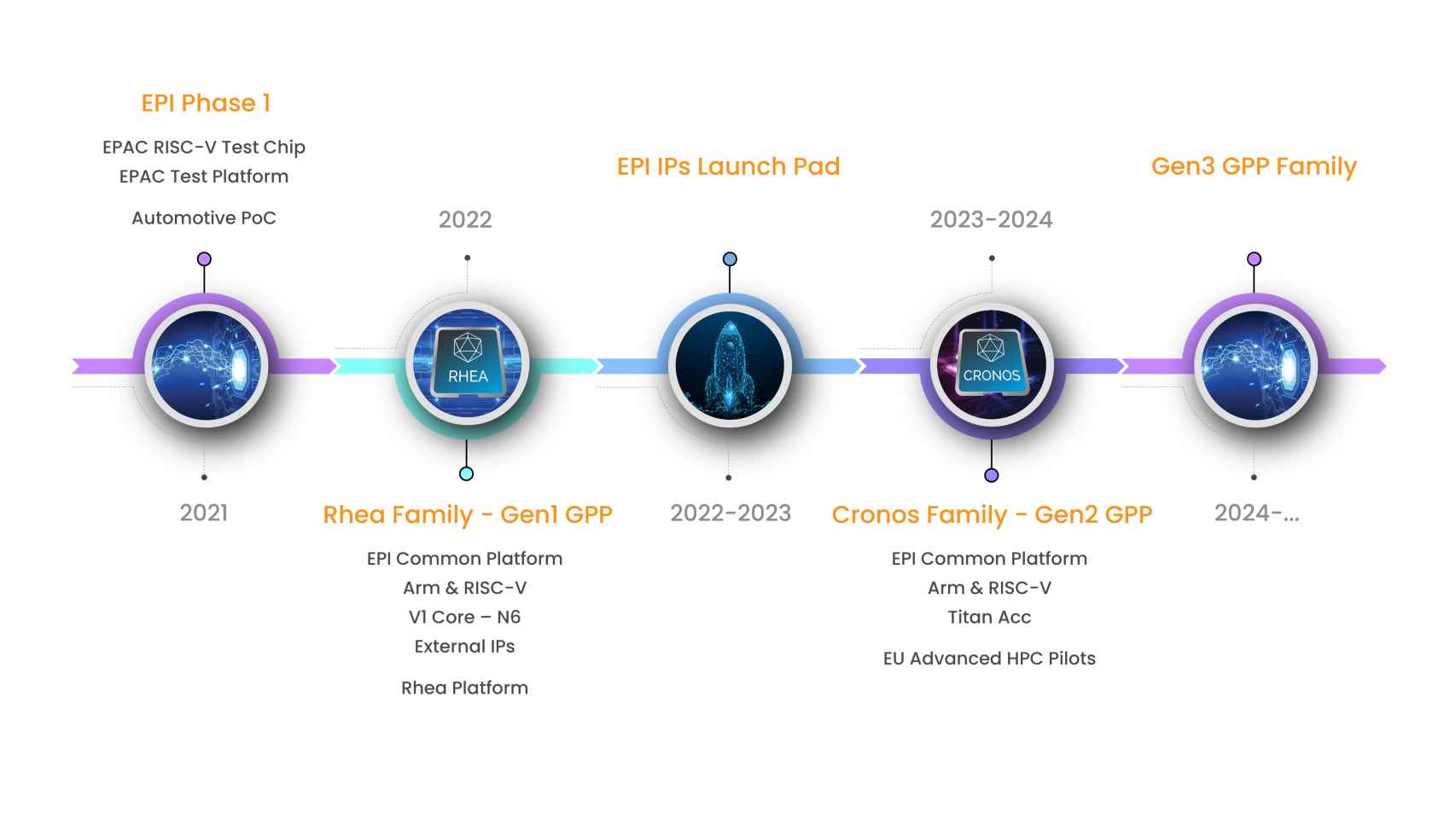

Hace unos días, la EPI anunciaba que esta fase se ha completado y la primera versión del nuevo procesador, denominado Rhea, está lista. Tras este éxito, en enero comenzará la segunda etapa de esta iniciativa: probar este chip de fabricación europea en prototipos de máquinas de exaescala –con 1.000 billones de operaciones por segundo– para lanzar versiones finales en 2023.

De forma paralela, también se ha diseñado y desarrollado un acelerador HPC personalizado conocido como EPAC (European Processor Accelerator) y un microcontrolador integrado para aplicaciones en el sector de la automoción.

Detrás de la EPI hay un consocio formado por 28 socios de 10 países europeos. Entre ellos, el Barcelona Supercomputing Center-Centro Nacional de Supercomputación (BSC-CNS), de España.

Rhea, el primer prototipo

Rhea es la primera generación del Procesador de Propósito General (GPP, por sus siglas en inglés) de la EPI. Tiene 29 núcleos RISC-V y se basa en la arquitectura ARM Neoverse V1. Detrás de su desarrollo y fabricación están la empresa francesa SiPearl, creada dentro del consorcio, y la multinacional Atos.

Para dar vida al proyecto, que cuenta con financiación del programa Horizonte 2020, “trabajamos en estrecha colaboración con los 28 socios de la iniciativa: la comunidad científica, centros de supercomputación, líderes de la industria y empresas innovadoras”, explica Philippe Notton, fundador y director ejecutivo de SiPearl.

Hoja de ruta de la EPI (European Processor Initiative).

En esta primera fase también se han diseñado funciones de seguridad de última generación. Esto incluye la IP desarrollada por ProvenRun, certificada para HPC y edge computing. Para reforzar aún más la seguridad, la Universidad de Pisa (Italia) contribuyó con una IP cifrada, llamada Crypto Tile, que SiPearl ha integrado en el GPP de Rhea.

Eficiencia energética y orgullo europeo

Dada la importancia tanto de reducir la huella de carbono de los sistemas informáticos de próxima generación como de alcanzar mayores capacidades de cálculo, la eficiencia energética ha sido clave.

Para este propósito, la Universidad de Bolonia (Italia) y ETH Zurich (Suiza) diseñaron un controlador de energía de código abierto basado en RISC-V, que se ha integrado en el procesador Rhea aprovechando algoritmos de control avanzado e inteligencia artificial.

“Estamos orgullosos de nuestro éxito en el diseño de un potente GPP que aprovecha las tecnologías de vanguardia y las IP creadas e implantadas exclusivamente por universidades europeas y líderes industriales”, afirma Emmanuel Ego, director de proyectos ASIC (Application Specific Integrated Circuits) en Atos.

“Confiamos en que pronto demostraremos el papel fundamental de este GPP en la habilitación de una máquina informática de exaescala europea, el próximo avance en el dominio de HPC que el mundo espera”, añade.

“Con el lanzamiento del procesador Rhea, todos contribuiremos a garantizar la soberanía europea en la computación de alto rendimiento para la medicina personalizada, el cambio climático y la gestión energética”, asegura el máximo responsable de SiPearl.

Listo para la conducción autónoma

La primera prueba de concepto de la tecnología, como se adelantaba más arriba, se ha realizado en el sector de la automoción para evaluar la viabilidad de la conducción autónoma.

En ella han participado la austriaca Infineon, con el desarrollo de una plataforma de cómputo integrado de alto rendimiento (eHPC) y un kit de desarrollo de software (SDK). Para llevarla a cabo se usó un BMW X5, un todoterreno del fabricante alemán de coches.

Coche de pruebas BMW X5 y el sistema informático EPI en el bastidor.

Se realizaron varios test para recopilar datos y valorar diferentes escenarios. Entre otras características, la plataforma incluye cámaras integradas compatibles con inteligencia artificial y software de Elektrobit (empresa alemana especializada en el desarrollo de soluciones para el automóvil) para el análisis de imágenes.

Los resultados revelan que la EPI tiene tecnologías adecuadas para la conducción autónoma hasta el nivel 4, donde el vehículo conduce de forma independiente la mayor parte del tiempo sin necesidad de intervención humana.

“Estoy orgulloso de los excelentes resultados obtenidos por los equipos de EPI después de sólo tres años de cooperación, allanando el camino hacia la soberanía tecnológica de Europa”, ha manifestado el presidente de EPI, Eric Mochalin.

“Esto ha creado condiciones favorables para el lanzamiento de la siguiente fase y la entrega exitosa de los procesadores y aceleradores europeos para los proyectos EUPEX (EUropean Pilot para Exascale) y TEP (The European Pilot), los precursores de los sistemas europeos de exaescala". El siguiente plazo fijado es 2024, cuando se espera que esté listo Cronos, la segunda generación del procesador íntegramente europeo.

Barcelona Supercomputing Center

La participación española del BSC-CNS ha tenido que ver con el diseño y desarrollo de EPAC, el acelerador HPC personalizado basado en la arquitectura de código abierto RISC-V. El fin es demostrar que se puede crear un diseño exclusivamente europeo de alto rendimiento y con un bajo coste energético.

“Los socios de toda Europa se han unido para crear algo que ninguna organización podría haber logrado por sí sola. Al trabajar con tecnologías y proyectos de código abierto, el flujo de EPAC ha ayudado a expandir el ecosistema RISC-V, haciendo que esta tecnología sea viable para un número de aplicaciones cada vez mayor en el futuro”, asevera Jesús Labarta, director de Ciencias de la Computación de BSC-CNS.