36-core-chip

El MIT desarrolla un chip de 36 núcleos con un diseño inspirado en Internet

Hace un par de días os hablamos de The Machine, tampoco hace mucho de la próxima conexión WiFi y también de una memoria USB tan rápida como un SSD. El que no corre vuela, y es que hoy os traemos una nueva noticia desde el Simposio Internacional de Arquitectura Informática: un nuevo chip de 36 núcleos basado en los routers de Internet.

El problema de los buses

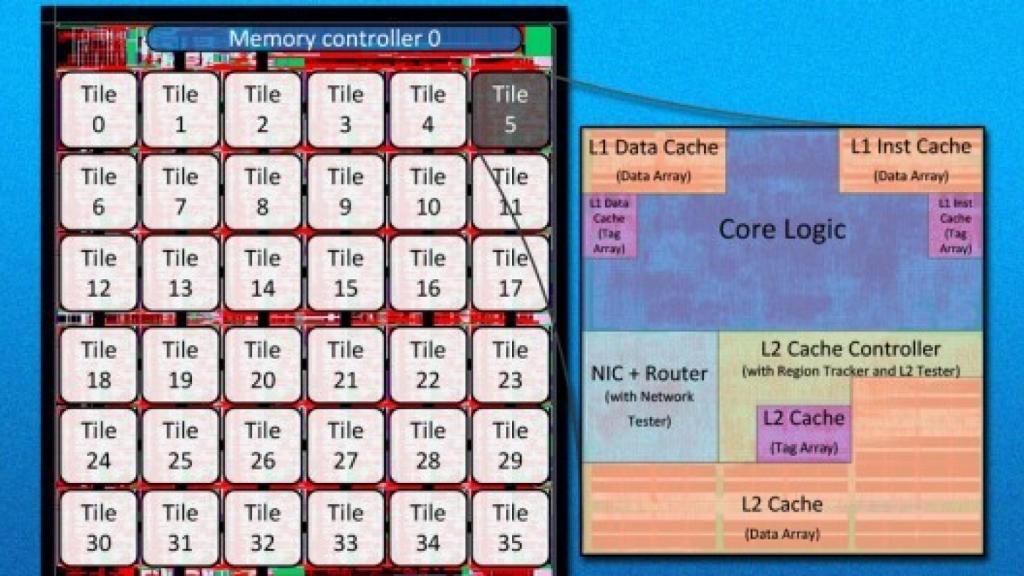

Cuanto mayor es el número de núcleos, mayor es el problema de comunicación entre ellos. Durante años, el investigador Li-Shiuan Peh, del MIT, siempre estuvo seguro de que los chips multi-núcleo se parecerían al Internet, donde cada núcleo tiene un router asociado y en el que los paquetes viajan entre núcleos.

Los chips multi-núcleo suelen ser más rápidos ya que pueden dividir la carga en varios trozos y ejecutarla en paralelo. No todas las tareas pueden dividirse en partes iguales y llevarse de manera independiente, por lo que los núcleos a veces necesitan compartir datos entre ellos. Normalmente, esto se hace a través de un único canal llamado “bus”, que en cuanto empieza a ser usado por dos núcleos que se comunican, deja de estar disponible para el resto.

Actualmente, los chips tienen entre dos y ocho núcleos, y ya se ven limitados por la arquitectura de un solo bus. En el futuro, será complicado mantener este concepto si verdaderamente se quiere ampliar el número de núcleos.

La red en un chip

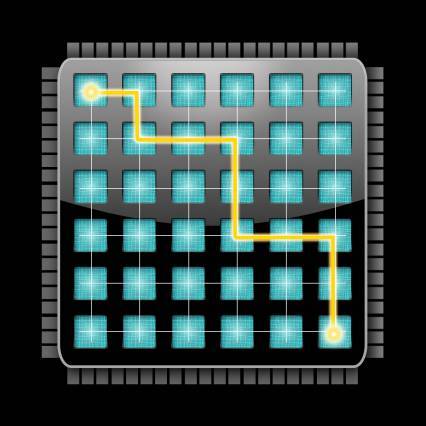

La propuesta del grupo de Peh se basa en la manera en que los routers son capaces de encontrar varias rutas para que los datos viajen entre ellos, facilitando la comunicación y haciéndola más rápida y fluida.

internet-chip

En lugar de depender de un solo bus, cada núcleo será capaz de comunicarse con los cuatro de al lado. En teoría, la conexión se haría con cables de pequeña longitud, por lo que el consumo energético también es menor.

Una caché eficiente

Con el fin de acelerar el envío de datos desde un núcleo hasta la memoria principal, cada uno contará con su propia caché, pequeña pero de altísima velocidad. El problema es que dos núcleos podrían estar modificando los mismos datos y al mismo tiempo, por lo que es necesario mantener la coherencia entre las memorias caché.

Hasta ahora, este problema se ha solventado con el “bus sniffing”, una técnica en el que el núcleo controla el bus de comunicación para que nadie más acceda a sus datos. Pero claro, hemos eliminado el bus, ¿y ahora qué?.

Por ahora, la solución ha sido una segunda red “sombra” que envía notificaciones a lo largo del chip para impedir que dos núcleos pidan un mismo paquete de datos. Lo mismo se hace en una red de routers, en la que existe un orden jerárquico/cronológico en el que se envían los pedidos a través del bus estándar.

Los investigadores planean evaluar la velocidad y rendimiento de su nuevo chip en Linux para después facilitar el código fuente a desarrolladores que quieran elaborar un modelo comercial en un futuro próximo. Como siempre, sólo nos toca esperar.

Fuente | MIT